TECHNOLOGY

BROKER

Spain

UNIVERSIDAD

POLITÉCNICA

DE MADRID

## Patentes Promocionadas

PONS IP

ESA Space IP Market Day

## EJEMPLOS PATENTES DE LA ESA DISPONIBLES PARA LA CONCESIÓN DE LICENCIAS

TRES familias de patentes relacionadas con la detección y el manejo de fallos en sistemas de comunicación diferencial, específicamente en el contexto de buses de señalización y controladores para comunicaciones de baja tensión. Cada uno aborda diferentes aspectos de estos sistemas, proporcionando métodos y circuitos para garantizar la integridad y eficiencia de la comunicación:

**PAT1: DETECTOR DE CALIDAD DE ENLACE DE COMUNICACIÓN DIFERENCIAL POR CABLE Y MÉTODO DE

DETECCIÓN DE CALIDAD DE ENLACE DE COMUNICACIÓN DIFERENCIAL POR CABLE**

**PAT2: CONTROLADOR CMOS TOLERANTE A ALTA TENSIÓN PARA BUSES DE COMUNICACIÓN

BIDIRECCIONAL DE BAJA TENSIÓN**

**PAT3: ARQUITECTURA DEL TRANSCEPTOR DE DETECCIÓN DE FALLAS DE BUS Y MÉTODO DE

OPERACIÓN DEL TRANSCEPTOR**

## CONTEXTO TECNOLÓGICO

Los sistemas de comunicación diferencial son métodos de transmisión de datos en los que las señales se envían a través de pares de conductores que transportan señales de fase opuesta (diferenciales). Este tipo de comunicación es esencial en **aplicaciones satelitales** debido a sus ventajas en términos de inmunidad al ruido y capacidad para mantener la integridad de la señal a largas distancias debido a su capacidad para proporcionar una transmisión de datos robusta y sin ruido. Esto es crucial para el éxito de las misiones espaciales y el funcionamiento continuo de los satélites.

Juntas, estas tres patentes forman un conjunto coherente de tecnologías destinadas a **mejorar la fiabilidad y la eficiencia de los sistemas de comunicación diferencial**.

A través de la detección y gestión de fallos, así como la optimización de la conmutación de voltaje, **estas innovaciones garantizan** que los buses de señalización y **los enlaces de comunicación** funcionen de manera robusta y eficiente en una variedad de aplicaciones tecnológicas.

## CARACTERÍSTICAS PRINCIPALES

- **Inmunidad al ruido:** Al transmitir señales que son de fase opuesta (una señal positiva y su inversa), los sistemas de comunicación diferencial pueden cancelar el ruido electromagnético que afecta a ambas señales por igual. Esto es crucial en el entorno espacial, donde las señales pueden ser perturbadas por la radiación cósmica y otros ruidos electromagnéticos.

- **Reducción de interferencias:** Dado que las señales diferenciales generan menos radiación electromagnética, es menos probable que interfieran con otros sistemas de comunicación a bordo del satélite o con otros satélites cercanos.

- **Integridad de la señal:** La transmisión diferencial ayuda a mantener la integridad de la señal a largas distancias, lo cual es vital para las comunicaciones entre satélites y estaciones terrestres, o entre diferentes componentes del mismo satélite.

- **Uso de pares trenzados:** Los sistemas de comunicación diferencial suelen utilizar cables de par trenzado. Esta estructura física contribuye aún más a la cancelación de ruido y a la reducción de interferencias.

## CAMPOS DE APLICACIÓN

### Aeronáutica y Aeroespacial

- o Sistemas Satelitales: Como se mencionó anteriormente, para telemetría, control y transmisión de datos científicos.

- o Aeronaves y Drones: Comunicación entre diferentes sistemas embarcados y con estaciones de control en tierra.

### Telecomunicaciones

- o Redes de datos: En la transmisión de datos de alta velocidad a través de cables de par trenzado, como Ethernet y otras tecnologías de red.

- o Telefonía: Para reducir el ruido y las interferencias en las líneas telefónicas.

### Electrónica de consumo

- o Conexiones USB y HDMI: Utilizan la comunicación diferencial para transmitir datos y señales de vídeo y audio de alta calidad.

- o Dispositivos móviles: En conexiones internas entre componentes como pantallas, cámaras y procesadores.

## CAMPOS DE APLICACIÓN (Cont.)

### Automotriz

- o Redes de comunicación del vehículo (CAN, LIN, FlexRay): Se utilizan para la comunicación entre diferentes módulos electrónicos del vehículo.

- o Sistemas de Entretenimiento y Navegación: Para la transmisión de señales de audio, video y datos dentro del automóvil.

### Informática y Tecnología de la Información:

- o Placas base y periféricos: Conexiones entre diferentes componentes del ordenador, como procesadores, memorias y tarjetas de expansión.

- o Centros de Datos: En conexiones de alta velocidad entre servidores y dispositivos de almacenamiento.

### Medicina y equipo de diagnóstico:

- o Equipos de imágenes médicas: como imágenes por resonancia magnética (IRM) y tomografía computarizada (TC), que requieren una transmisión de datos sin ruido.

- o Monitorización de Pacientes: Sistemas de monitorización que necesitan transmitir señales biomédicas con alta fidelidad.

## CAMPOS DE APLICACIÓN (Cont.)

### Industria y automatización

- o Control de Procesos Industriales: En comunicación entre sensores, actuadores y controladores en entornos industriales ruidosos.

- o Robótica: Para la transmisión de señales de control y datos entre los diferentes componentes de los robots industriales.

### Sistemas de distribución de energía y energía

- o Smart Grids: En comunicación entre dispositivos de monitorización y control en redes inteligentes.

- o Inversores y Convertidores de Energía: Para la transmisión de señales de control en sistemas de energías renovables como paneles solares y turbinas eólicas.

### Defensa y seguridad

- o Sistemas de Comunicación Militar: En redes de comunicación seguras y resistentes al ruido para aplicaciones críticas.

- o Sistemas de Vigilancia y Detección: Para asegurar la transmisión de datos en sistemas de radar y otros dispositivos de detección.

# PAT1: DETECTOR DE CALIDAD DE ENLACE DE COMUNICACIÓN DIFERENCIAL POR CABLE Y MÉTODO DE DETECCIÓN DE CALIDAD DE ENLACE DE COMUNICACIÓN DIFERENCIAL POR CABLE

## Title

[EN] DIFFERENTIAL WIRED COMMUNICATION LINK QUALITY DETECTOR AND DIFFERENTIAL WIRED COMMUNICATION LINK QUALITY DETECTION METHOD

## Abstract

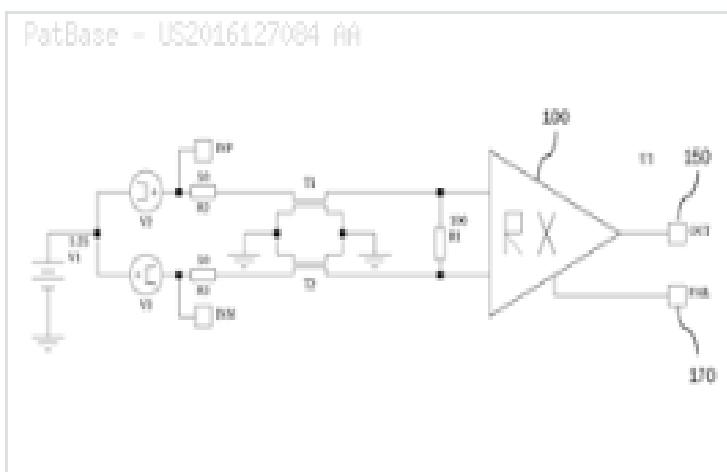

[EN] A method of determining link failure in a receiver for receiving a differential voltage signal via a first signal line and a second signal line, the method including: obtaining a first quantity depending on the larger one of a maximum value over time of a voltage level that is attained in the first signal line and a maximum value over time of a voltage level that is attained in the second signal line; obtaining a second quantity depending on a maximum value over time of an average of an instantaneous voltage level in the first signal line and an instantaneous voltage level in the second signal line; and determining that the link failure has occurred on the basis of the first quantity and the second quantity.

## AI Summary

- This method helps identify when a communication link between devices has failed by analyzing the voltage levels in two signal lines that carry important information.

- It uses two different calculations: one looks at the highest voltage levels reached over time, while the other averages the instantaneous voltage levels, providing a comprehensive view of the signal's health.

- The novelty lies in combining these two approaches to improve the accuracy of detecting failures, ensuring that devices can respond quickly and maintain reliable communication.

# PAT1: DETECTOR DE CALIDAD DE ENLACE DE COMUNICACIÓN DIFERENCIAL POR CABLE Y MÉTODO DE DETECCIÓN DE CALIDAD DE ENLACE DE COMUNICACIÓN DIFERENCIAL POR CABLE

El detector de calidad de enlace de comunicación por cable diferencial y el método de detección de calidad de enlace de comunicación por cable diferencial abordan la detección de la calidad del enlace de comunicación diferencial. Propone un método y un aparato para identificar fallos en un receptor que recibe señales de tensión diferencial. Las fallas pueden ser de varios tipos, como cortocircuitos o fallas abiertas en una o ambas líneas de señal. El método evalúa las variaciones de voltaje en las líneas de señal y determina la ocurrencia de fallas en función de estas mediciones, manteniendo así la integridad del enlace de comunicación.

## Ventajas

| Característica                   | Monitores de enlace tradicionales  | EP3018830A1 Detector                                       |

|----------------------------------|------------------------------------|------------------------------------------------------------|

| Velocidad de detección de fallos | Lento (basado en protocolos)       | En tiempo real (nivel de hardware)                         |

| Tipos de errores detectados      | Limitado                           | Cortocircuitos, circuitos abiertos, distorsión de la señal |

| Dependencia del protocolo        | Requiere procesamiento de software | Funciona de forma independiente en la capa física          |

| Rendimiento energético           | Mayor consumo de energía           | Optimizado para funcionamiento a baja potencia             |

| Idoneidad para entornos hostiles | Limitado                           | Entornos resistentes a la radiación y de alto ruido        |

# PAT1: DETECTOR DE CALIDAD DE ENLACE DE COMUNICACIÓN DIFERENCIAL POR CABLE Y MÉTODO DE DETECCIÓN DE CALIDAD DE ENLACE DE COMUNICACIÓN DIFERENCIAL POR CABLE

## Competidores

- ROSEMOUNT INC (13 citations)

- ROHM CO LTD (4 citations)

- ST MICROELECTRONICS INT NV (2 citations)

- NXP SEMICONDUCTORS NV (1 citations)

- ZIBO ZHIXING ELECTRONIC TECH CO LTD (1 citations)

Family [Family Explorer](#)

| Publication number | Publication date | Application number | Application date |  |  |  |  |

|--------------------|------------------|--------------------|------------------|--|--|--|--|

| DE602014010710 D1  | 20170727         | DE201460010710T    | 20141105         |  |  |  |  |

| EP3018830 A1       | 20160511         | EP20140191802      | 20141105         |  |  |  |  |

| EP3018830 B1       | 20170614         | EP20140191802      | 20141105         |  |  |  |  |

| ES2637774 T3       | 20171017         | ES20140191802T     | 20141105         |  |  |  |  |

| US2016127084 AA    | 20160505         | US20150933864      | 20151105         |  |  |  |  |

| US9544103 BB       | 20170110         | US20150933864      | 20151105         |  |  |  |  |

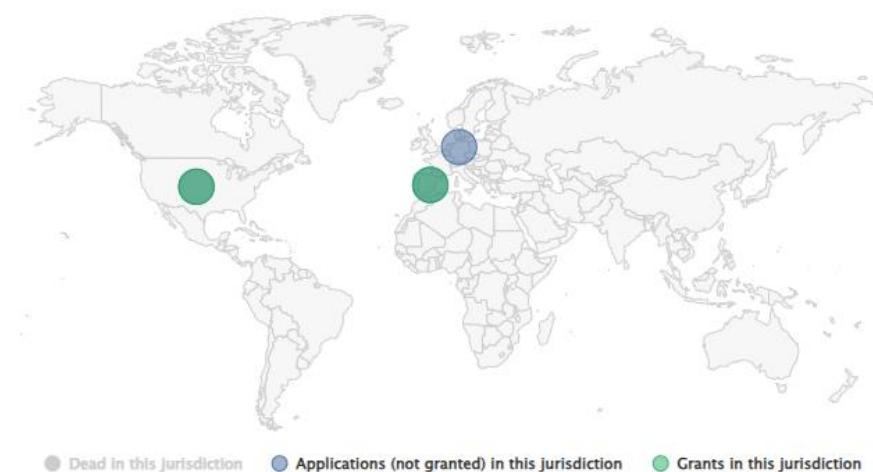

(● Dead in this Jurisdiction   ● Applications (not granted) in this jurisdiction   ● Grants in this jurisdiction)

PONS IP<sub>10</sub>

# PAT1: DETECTOR DE CALIDAD DE ENLACE DE COMUNICACIÓN DIFERENCIAL POR CABLE Y MÉTODO DE DETECCIÓN DE CALIDAD DE ENLACE DE COMUNICACIÓN DIFERENCIAL POR CABLE

## DIFFERENTIAL WIRED COMMUNICATION LINK QUALITY DETECTOR AND DIFFERENTIAL WIRED COMMUNICATION LINK DETECTION

SHARE — X F in

PATENT CATEGORY

**ELECTRONICS AND OPTOELECTRONICS**

REFERENCE #

**645**

PATENT COMPETENCE DOMAIN

**CD 3: AVIONIC ARCHITECTURE / DHS / ONBOARD S/W / FDIR / GNC / AOCS / TT&C (E2E)**

### ABSTRACT

This invention relates to a LVDS receiver capable of detecting link failure, be it a single short failure, double short failure, single open failure, or double open failure. The invention proposes a method of determining this link failure in 3 steps using a peak detector, which is more noise resilient and a comparator only, instead of the common 3 comparators used in other market products. Moreover, the proposed solution is also characterized by providing a simplified and more compact design, with reduced overall costs and improved system reliability.

### Description

The fail-safe circuit presented here assesses the quality of the signal or potential link failure modes and provides a signal quality flag to take appropriate decisions when processing the received data. This is done with integrated circuits that monitor and measure incoming signal levels, amplitude, strength and impedances and then perform the appropriate control actions over the incoming and outgoing signals. The latter can range from blocking the incoming data stream to for example switching to the redundant communication link or enabling higher communication level protocol error detection and correction schemes. The link failures that can be detected with the proposed fail-safe circuits are:

- a) single short failure: one input line short circuited to a fixed voltage

- b) double short failure: both input lines are short circuited to a fixed voltage

- c) single open failure: one input line has a broken connection (is disconnected). Both small and high capacitive loads at the input of the LVDS receiver are cases where the open failure should be detected.

- d) double open failure: both input lines are disconnected, due to either a cable rupture

### Innovations and advantages:

The techniques commonly used in LVDS receivers are known to induce noise and self-oscillations to the data transmission that corrupt it and, for some applications, these are crucial factors. In order to minimize this effect and provide link failure detection, this invention proposes a new approach characterized by:

- Using a peak detector which is more noise resilient than the window comparator, used in other solutions.

- Only 1 comparator is needed instead of 3.

- Simplified design due to using fewer components and not requiring external hardware.

- Reduced dimensions and materials used.

- Reduced manufacturing costs.

- Improved reliability of the overall system.

### Commercialisation aspects

#### Applications and Markets

This invention is useful for any application that uses LVDS, such as any electronic system that requires the communication between different parts (peripherals and a processor).

- Machine vision. This invention could be used to improve the signals received by machines to their vision systems, thus improving their perception of the environment and their autonomy.

- Other peripherals. Aside from vision and display peripherals, LVDSs are also used for interconnecting the processing unit to other peripherals, such as memory units. It could present strong benefits for applications on super-computers.

- Bio-medicine. Applications (such as DNA micro-array analysis, mass spectrometry and confocal microscopy, among others) where the data gathered is highly sensitive to noise, be it because of the low values or the precision required.

<https://commercialisation.esa.int/patents/>

### COMPETENCE DOMAINS

- CD 2: STRUCTURES / MECHANISMS / MATERIALS / THERMAL

- CD 3: AVIONIC ARCHITECTURE / DHS / ONBOARD S/W / FOIR / GNC / AODCS / TT&C (E2E)

- CD 4: ELECTRIC ARCHITECTURE / POWER & ENERGY / EMC

- CD 5: END-TO-END RF & OPTICAL SYSTEMS / PRODUCTS FOR NAVIGATION, COMM. & REMOTE SENSING

- CD 6: LIFE / PHYSICAL SCIENCE PAYLOADS / LIFE SUPPORT / ROBOTICS AND AUTOMATION

- CD 7: PROPULSION, SPACE TRANSPORTATION AND RE-ENTRY VEHICLES

- CD 8: GROUND DATA SYSTEMS / MISSION OPERATIONS

- CD 10: ASTRODYNAMICS / SPACE DEBRIS / SPACE ENVIRONMENT

COMPANIES INTERESTED IN MAKING USE OF AN ESA PATENT CAN GET IN CONTACT WITH [PATENT@ESA.INT](mailto:PATENT@ESA.INT).

[CONTACT US](#)

Search...

**CATEGORIES**

- AUTOMATION AND ROBOTICS

- COMMUNICATION AND INFORMATION

- DIGITALISATION, COMPUTER HARDWARE AND SOFTWARE

- ELECTRONICS AND OPTOELECTRONICS

- MECHANICAL COMPONENTS AND SYSTEMS

- OTHER

- SENSORS AND MEASUREMENT TECHNIQUES

- SERVICES

**COMMUNICATION AND INFORMATION**

**CD 5: END-TO-END RF & OPTICAL SYSTEMS / PRODUCTS FOR NAVIGATION, COMM. & REMOTE SENSING**

#794 Reconfigurable Digital Beamforming Network

---

**COMMUNICATION AND INFORMATION**

**CD 5: END-TO-END RF & OPTICAL SYSTEMS / PRODUCTS FOR NAVIGATION, COMM. & REMOTE SENSING**

#792 Transmit/receive multiple feed per beam single reflector antenna

---

**COMMUNICATION AND INFORMATION**

**CD 5: END-TO-END RF & OPTICAL SYSTEMS / PRODUCTS FOR NAVIGATION, COMM. & REMOTE SENSING**

#789 Syntonization of Signals Between Satellites

---

**COMMUNICATION AND INFORMATION**

# PAT2: CONTROLADOR CMOS TOLERANTE A ALTA TENSIÓN PARA BUSES DE COMUNICACIÓN BIDIRECCIONAL DE BAJA TENSIÓN

[EN] HIGH VOLTAGE TOLERANT CMOS DRIVER FOR LOW-VOLTAGE BI-DIRECTIONAL COMMUNICATION BUSES

## Abstract

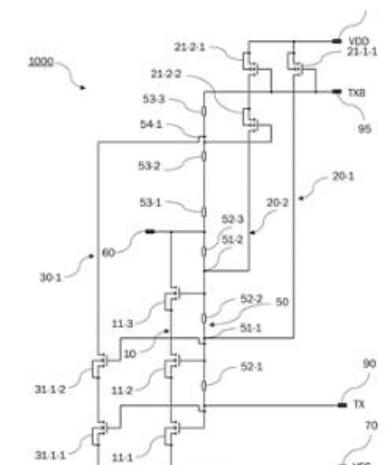

[EN] This application relates to a bi-state driver circuit for switching an output terminal between a first predetermined voltage level and a high impedance state. The bi-state driver circuit comprises a first string of transistors connected between the output terminal and the first predetermined voltage level and comprising at least a first transistor arranged closer to the first predetermined voltage level and a second transistor arranged closer to the output terminal, a voltage divider circuit connected between the output terminal and a voltage level of a control signal attaining voltage levels between the first predetermined voltage level and a second predetermined voltage level, comprising at least one intermediate node having an intermediate voltage level between a voltage level of the output terminal and the voltage level of the control signal, and a second string of transistors connected between the intermediate node of the voltage divider circuit and the second predetermined voltage level, and comprising at least a third transistor. A control terminal of the second transistor is connected to the intermediate node. The first transistor is configured to be switched in accordance with the control signal. The third transistor is configured to be switched in accordance with the control signal, in a phase-locked relationship with the first transistor. The application further relates to a driver circuit for switching a first output terminal between a first output voltage level and a high impedance state, and for switching a second output terminal between a second output voltage level and the high impedance state. The application yet further relates to a method of controlling a bi-state driver circuit.

## AI Summary

- This bi-state driver circuit allows electronic devices to efficiently switch between two different voltage levels and a high impedance state, which helps in managing power consumption and signal integrity.

- The innovative design uses multiple transistors and a voltage divider to create a precise control mechanism, ensuring that the output can be finely tuned based on the control signal.

- By enabling simultaneous control of multiple output terminals, this technology enhances the performance and versatility of electronic systems, making them more adaptable to various applications.

## PAT2: CONTROLADOR CMOS TOLERANTE A ALTA TENSIÓN PARA BUSES DE COMUNICACIÓN BIDIRECCIONAL DE BAJA TENSIÓN

Se centra en un controlador CMOS tolerante a alto voltaje optimizado para buses de comunicación bidireccionales de bajo voltaje. Este controlador biestable cambiará un terminal de salida entre un nivel de voltaje predeterminado y un estado de alta impedancia. Utiliza un divisor de voltaje y una cadena de transistores que operan en fase con la señal de control, lo que garantiza una conmutación precisa y eficiente en sistemas de comunicación sensibles al voltaje.

Concedido y en vigor en EE. UU., DE, ES, FR, GB, SE.

### Ventajas

| Característica                        | Controladores CMOS tradicionales   | Conductor EP3311489A1                                    |

|---------------------------------------|------------------------------------|----------------------------------------------------------|

| Tolerancia de voltaje                 | Voltaje de alimentación de 2x a 3x | Hasta 6x tensión de alimentación                         |

| Rendimiento energético                | Consumo continuo de energía        | Desactivación automática en estado inactivo              |

| Soporte multiterminal                 | Limitado                           | Admite el funcionamiento simultáneo de varios terminales |

| Protección contra rebotes en el suelo | Mínimo                             | Compensación de voltaje avanzada                         |

| Compatibilidad CMOS de bajo voltaje   | Requiere CMOS de alto voltaje      | Funciona con CMOS estándar de 3,3 V                      |

| Gestión térmica                       | Alta disipación de calor           | Menor pérdida de energía, menos calor                    |

# PAT2: CONTROLADOR CMOS TOLERANTE A ALTA TENSIÓN PARA BUSES DE COMUNICACIÓN BIDIRECCIONAL DE BAJA TENSIÓN

## Competidores

- INTEL CORP (2229 publications)

- SAMSUNG ELECTRONICS CO LTD (1510 publications)

- IBM (1175 publications)

- QUALCOMM INC (1069 publications)

- HUAWEI TECHNOLOGIES CO LTD (700 publications)

- AVAGO TECHNOLOGIES LTD (699 publications)

- MICRON TECHNOLOGY INC (691 publications)

- FUJITSU LTD (452 publications)

- RENESAS ELECTRONICS CORP (301 publications)

- TEXAS INSTRUMENTS INC (286 publications)

Family Family Explorer

| Publication number | Publication date | Application number | Application date |                                                                                                                                                                                                                                                                                                                                                 |

|--------------------|------------------|--------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DE602015072847 D1  | 20210923         | DE201560072847T    | 20150618         |     |

| EP3311489 A1       | 20180425         | EP20150730764      | 20150618         |                                                                                        |

| EP3311489 B1       | 20210901         | EP20150730764      | 20150618         |                                                                                                                                                                           |

| ES2898651 T3       | 20220308         | ES20150730764T     | 20150618         |                                                                                                                                                                           |

| US10637473 BB      | 20200428         | US20150737437      | 20150618         |                                                                                                                                                                           |

| US2018175859 AA    | 20180621         | US20150737437      | 20150618         |                                                                                                                                                                           |

| WO16202395 A1      | 20161222         | WO2015EP63761      | 20150618         |                                                                                                                                                                           |

● Dead in this jurisdiction

● Applications (not granted) in this jurisdiction

● Grants in this jurisdiction

## PAT3: ARQUITECTURA DEL TRANSCEPTOR DE DETECCIÓN DE FALLAS DE BUS Y MÉTODO DE OPERACIÓN DEL TRANSCEPTOR

## Title

## [EN] BUS FAILURE DETECTION TRANSCEIVER ARCHITECTURE AND TRANSCEIVER OPERATION METHOD

## Abstract

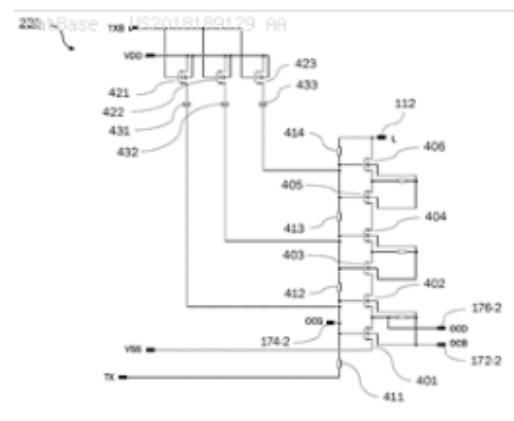

[EN] This application relates to a method of operating a transceiver for imparting a voltage signal on a differential signaling bus, wherein the transceiver comprises an output terminal and a string of one or more transistors connected between the output terminal and a predetermined voltage level, and wherein the transceiver can be switched between an active state in which the predetermined voltage level is applied to the output terminal, and an inactive state in which the predetermined voltage level is not applied to the output terminal. The method comprises a detection step of detecting a first quantity depending on a current flowing through a first transistor in the string of transistors, a failure determination step of determining whether the detected first quantity satisfies one or more error conditions, and a control step of switching the transceiver to the inactive state if the detected first quantity is determined to satisfy at least one of the one or more error conditions. The application further relates to a transceiver for imparting a voltage signal on a differential signaling bus.

## AI Summary

- This application introduces a smart way for a device to manage its power usage by switching off its signal output when it detects potential problems, helping to prevent damage and conserve energy.

- It uses a series of transistors to control the flow of electricity, allowing the device to quickly respond to issues by stopping the signal when necessary.

- The novelty lies in its ability to automatically detect electrical problems and take action, making devices more reliable and efficient in their communication.

PONS IP<sub>16</sub>

## PAT3: ARQUITECTURA DEL TRANSCEPTOR DE DETECCIÓN DE FALLAS DE BUS Y MÉTODO DE OPERACIÓN DEL TRANSCEPTOR

presenta una arquitectura de transceptor diseñada para la detección de fallos en un bus de señalización diferencial. El transceptor puede funcionar entre un estado activo e inactivo dependiendo de la detección de condiciones de error en la corriente que fluye a través de una cadena de transistores. Este sistema permite identificar fallos y responder de forma eficaz, garantizando la estabilidad del bus de comunicación.

Concedido y en vigor en EE. UU., AT, BE, CH, DE, ES, FR, GB, IT, LI, NL y SE.

### Ventajas

| Característica                              | Transceptores convencionales    | Transceptor de invención de la ESA       |

|---------------------------------------------|---------------------------------|------------------------------------------|

| <b>Velocidad de detección de fallos</b>     | Retrasado (nivel de protocolo)  | Inmediato (nivel de hardware)            |

| <b>Prevención de propagación de errores</b> | Limitado                        | Aislamiento completo de fallos           |

| <b>Consumo de energía</b>                   | Siempre activo                  | Desactivación automática durante errores |

| <b>Manejo de voltaje</b>                    | Tolerancia limitada             | Resiliencia de alto voltaje (16 V)       |

| <b>Integración</b>                          | Requiere monitoreo por separado | Detección de fallos autónoma             |

## PAT3: ARQUITECTURA DEL TRANSCEPTOR DE DETECCIÓN DE FALLAS DE BUS Y MÉTODO DE OPERACIÓN DEL TRANSCEPTOR

### Competidores

- TEKTRONIX INC (9 citations)

- NXP SEMICONDUCTORS NV (8 citations)

- HUAWEI TECHNOLOGIES CO LTD (6 citations)

- STMICROELECTRONICS APPLICATION GMBH (4 citations)

- BEIJING INST CONTROL ENG (2 citations)

- BEIJING RUNKE GENERAL TECH CO LTD (2 citations)

- CN ACADEMY LAUNCH VEHICLE TECH (2 citations)

- SPACE STAR TECHNOLOGY CO LTD (2 citations)

Family [Family Explorer](#)

| Publication number | Publication date | Application number | Application date | R   | ⋮ |

|--------------------|------------------|--------------------|------------------|-----|---|

| DE602015066958 D1  | 20210408         | DE201560066958T    | 20150618         | R   | ⋮ |

| EP3311539 A1       | 20180425         | EP20150731030      | 20150618         | A R | ⋮ |

| EP3311539 B1       | 20210317         | EP20150731030      | 20150618         | A R | ⋮ |

| ES2872334 T3       | 20211102         | ES20150731030T     | 20150618         | A R | ⋮ |

| US10565042 BB      | 20200218         | US20150737455      | 20150618         | A R | ⋮ |

| US2018189129 AA    | 20180705         | US20150737455      | 20150618         | A R | ⋮ |

| WO16202396 A1      | 20161222         | WO2015EP63762      | 20150618         | A R | ⋮ |

| WO16202396 A8      | 20170309         | WO2015EP63762      | 20150618         | A R | ⋮ |

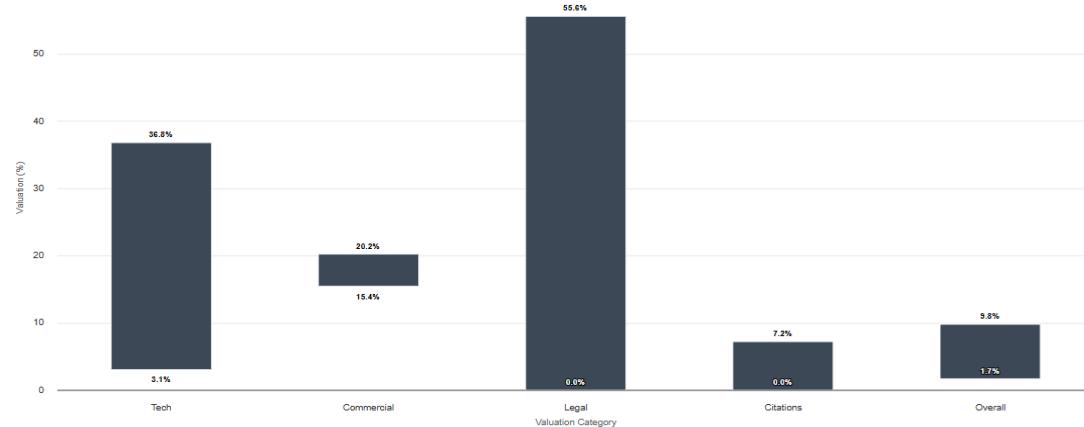

# PATENT VALUATION SCORE (PVS)

| Categoría | Puntaje (%) | Análisis                                                                                                                   |

|-----------|-------------|----------------------------------------------------------------------------------------------------------------------------|

| Técnica   | 36,8%       | Aceptable. Diversidad técnica.<br>Alcance moderado en términos de industrias y tecnología.                                 |

| Comercial | 15-20%      | Presencia comercial limitada: familia pequeña.                                                                             |

| Legal     | 55,6%       | Relativamente fuerte.<br>Buena cobertura legal, patentes aún vigentes, y con una estructura de reivindicaciones razonable. |

| Citas     | 7,2%        | Poco reconocimiento o impacto en el ecosistema de patentes.                                                                |

# PROSPECCIÓN DE EMPRESAS

| Rank ▾ | Type | Assignees           | INVESTMENT |                     |                    |                     | IMPACT               |                    |                            |  |

|--------|------|---------------------|------------|---------------------|--------------------|---------------------|----------------------|--------------------|----------------------------|--|

|        |      |                     | Inventions | Acquired inventions | Invention velocity | Presence as a shark | Litigated inventions | Opposed inventions | Non-self forward citations |  |

| 0.8    |      | Renesas Electronics | 87         | 10                  | 1                  | 3                   | 1                    | 1                  | 1256                       |  |

| 0.7    |      | Samsung Electronics | 163        | 0                   | 5.8                | 8                   | 3                    | 1                  | 1476                       |  |

| 0.7    |      | Marvell Asia        | 28         | 13                  | 0.8                | 15                  | 1                    | 0                  | 562                        |  |

| 0.7    |      | Analog Devices      | 39         | 0                   | 0.4                | 2                   | 2                    | 1                  | 652                        |  |

| 0.6    |      | Stmicroelectronics  | 39         | 4                   | 1.6                | 2                   | 0                    | 1                  | 570                        |  |

| 0.6    |      | Qualcomm            | 88         | 0                   | 1.8                | 32                  | 2                    | 0                  | 1974                       |  |

| 0.6    |      | Intel               | 90         | 7                   | 2                  | 9                   | 0                    | 1                  | 1736                       |  |

| 0.6    |      | Fujitsu             | 98         | 1                   | 0.6                | 6                   | 0                    | 1                  | 1306                       |  |

| 0.6    | ➡    | Commscope Techno... | 5          | 4                   | 0                  | 2                   | 0                    | 1                  | 226                        |  |

| 0.6    |      | Altera              | 12         | 2                   | 0                  | 3                   | 1                    | 0                  | 188                        |  |

| 0.5    |      | Mediatek            | 24         | 2                   | 0.4                | 6                   | 0                    | 0                  | 142                        |  |

PONS IP<sub>20</sub>

TECHNOLOGY

BROKER

Spain

UNIVERSIDAD

POLÍTÉCNICA

DE MADRID

# PONS IP

ESA Space IP Market Day